SRAM隨機存儲器的特點及結構

2020-04-28 09:20:30

隨著微電子技術的迅猛發展,

SRAM存儲器逐漸呈現出高集成度、快速及低功耗的發展趨勢。在半導體存儲器的發展中,靜態存儲器(SRAM)由于其廣泛的應用成為其中不可或缺的重要一員。下面由英尚微電子詳細介紹關于SRAM隨機存儲器的特點及結構。

SRAM隨機存儲器的特點

隨機存儲器最大的特點就是可以隨時對它進行讀寫操作,但當電源斷開時,存儲信息便會消失。隨機存儲器依照數據存儲方式的不同,主要可以分為動態隨機存儲器(DRAM)與靜態隨機存儲器(SRAM)兩大類。DRAM 以電容上存儲電荷數的多少來代表所存儲的數據,電路結構十分簡單(采用單管單電容1T-1C的電路形式),因此集成度很高,但是因為電容上的電荷會泄漏,為了能長期保存數據,它需要定期的刷新操作。這不但使DRAM 的讀寫控制變得復雜,而且也降低了它的讀寫速度。DRAM 主要用作主存儲器。SRAM 是依靠一對反相器以閉環形式連接的存儲電路,它的代碼的讀出是非破壞性的,并不需要相應的刷新電路,因此它的存取速度比DRAM 要快。但是,SRAM 需要用更多的晶體管來存儲一位的信息(采用六管單元或四管兩電阻單元儲存一位數據),因而其位密度比其它類型的低,造價也高。靜態存儲器多用于二級高速緩存。

SRAM隨機存儲器的結構

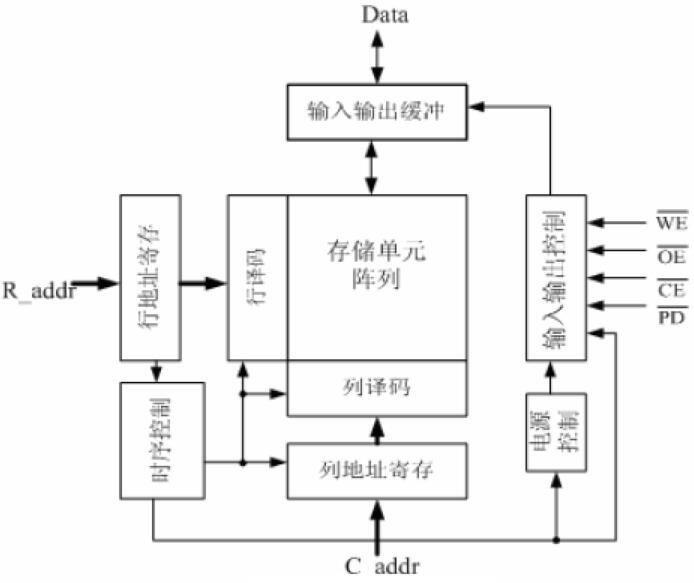

圖2.1 給出了SRAM的一般結構[1],主要包括存儲陣列、譯碼器、時序控制、輸入輸出緩沖、輸入輸出控制等。存儲陣列由存儲單元構成,用于保存數據,存儲陣列的布局對整個存儲器的面積、功耗、可靠性等有著非常重要的影響;由于存儲陣列是按行、列分開組織的,因此,譯碼器也分為行譯碼器和列譯碼器,并且地址譯碼之前,需要對地址進行緩存;輸入輸出緩沖是存儲陣列與外部數據交換的接口,用于放大存儲單元讀出的信號,以及將輸入信號寫入到存儲陣列之中;輸入輸出控制模塊根據控制信號的時序要求,控制存儲器的讀出、寫入等操作;電源控制是一個可選的電路單元,主要是為了低功耗的要求,當整個存儲器不需要進行讀寫操作時,通過電源控制可以控制內部無效的翻轉操作,從而節省功耗。完整的存儲結構中可能還包括測試電路模塊,例如內部監測電路、BIST電路等等。

圖1.1 SRAM 結構

圖1.2 存儲器的功能模型 圖1.3 存儲器的關鍵路徑

圖1.2 是SRAM的功能模型,圖1.3 給出了SRAM的關鍵路徑,也就是從地址輸入開始到數據輸出之間影響讀出操作的通路。為了更好地理解SRAM的關鍵路徑,首先對SRAM的讀寫過程進行初步的分析。以讀出操作為例,首先是讀信號和地址信號有效,然后在內部時序電路的控制下,對存儲陣列中的位線進行預充電,接下來行、列譯碼器輸出,選中相應的存儲單元的字線和位線,數據經靈敏放大器后到輸出緩沖器中,就完成了讀出操作的全過程。顯然圖1.3 的關鍵路徑就充分反映了這個過程。

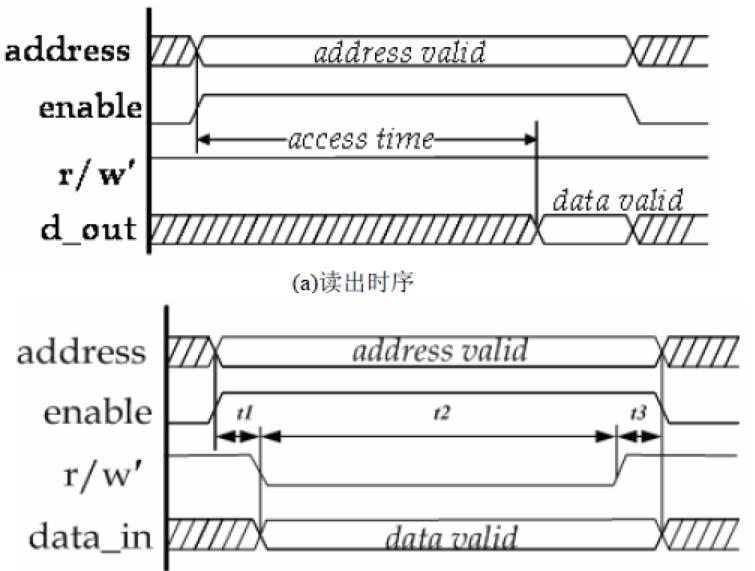

圖1.4 給出了

SRAM存儲器的讀寫時序。在讀出操作中,訪問時間(access time)就是指從地址有效算起,到有效數據輸出的時間;圖1.4 (b)中t1 是從地址和使能信號穩定到寫信號有效所需的最小時間,t2 是寫信號無效之前必須保持的最小時間,t3是寫信號無效之后地址信號仍需保持的最小時間。t1、t2、t3 相加就是一個寫周期時間。

圖1.4 存儲器的讀寫時序

以上對

VTI代理英尚微電子對SRAM的結構、操作進行了簡單地介紹和分析。

本文關鍵詞: SRAM SRAM隨機存儲器

相關文章:?靜態隨機存儲器SRAM存儲數據原理

深圳市英尚微電子有限公司是一家專業的靜態隨機記憶體產品及方案提供商,十年來專業致力代理分銷存儲芯片IC, SRAM、MRAM、pSRAM、 FLASH芯片、SDRAM(DDR1/DDR2/DDR3)等,為客人提供性價比更高的產品及方案。

英尚微電子中國區指定的授權代理:VTI代理、NETSOL、JSC濟州半導體(EMLSI)、Everspin 、IPSILOG、LYONTEK、ISSI、CYPRESS、ISOCOME、PARAGON、SINOCHIP、UNIIC; 著名半導體品牌的專業分銷商 如:RAMTROM、ETRON、FUJITSU、LYONTEK、WILLSEMI。

?更多資訊關注SRAMSUN. www.sjbg.net.cn 0755-66658299