Xilinx FPGA控制器的Everspin STT-DDR4設計指南

2020-01-19 09:22:48

自旋轉移扭矩磁阻隨機存取存儲器(

STT-MRAM)是一種持久性存儲技術,可利用各種工業標準接口提供性能,持久性和耐用性。 Everspin推出了STT-MRAM產品,該產品利用稱為JE-DDR4的JEDEC標準DDR4接口的變體,它包含了對完整系統支持所需的獨特功能。本文將幫助工程師了解Xilinx FPGA控制器的Everspin STT-DDR4設計指南

2.啟用ST-DDR4

為了使設計人員能夠快速集成ST-DDR4支持,該過程從Xilinx Vivado開發環境中生成的現有8Gb DDR4 SDRAM-2666存儲器接口生成器(MIG)開始。與8Gb DDR4 SDRAM的差異如下,并將在后續章節中進行說明:

1.時間安排(減少工作頻率,增加行訪問時間,增加計數器寬度并減小CAS頁面大小)

2.加電(校準–校準期間啟用了防亂涂模式)

3.掉電(將所有相關數據塞入或移動到持久性存儲器陣列中)

4.性能(增加管道深度并提高數據傳輸效率)

注意:健壯的ST-DDR4持久性存儲器設計還需要系統級的糾錯碼(ECC)方案,但該文檔不在本文范圍之內。

3. DDR4 SDRAM-1333內存接口

在Xilinx設計環境中,將根據代表8Gb

SDRAM DDR4-2666的速度和時序特性的輸入參數生成DDR4接口邏輯。

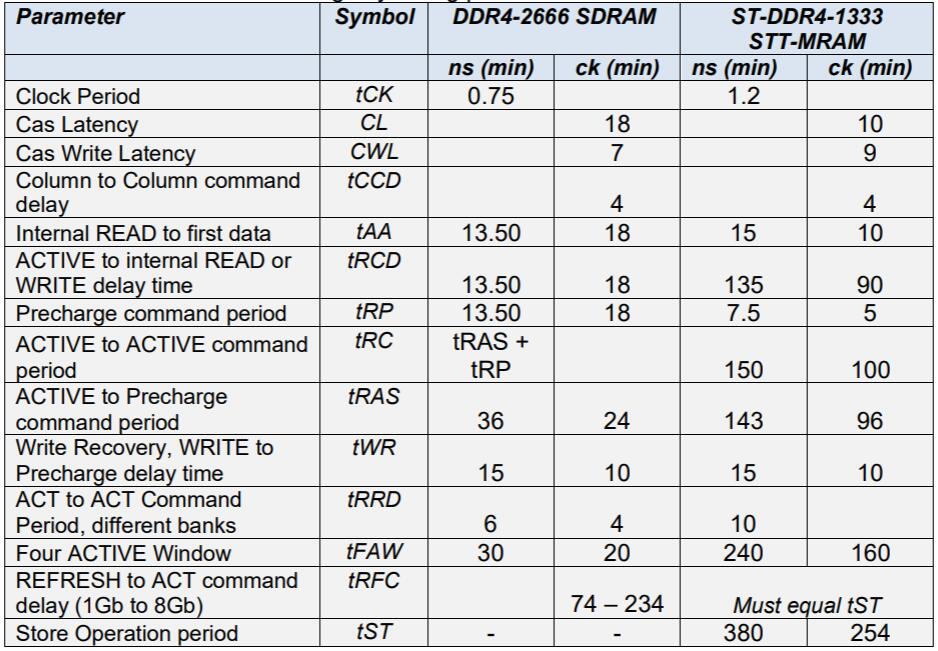

該表顯示了DDR4和ST-DDR4的關鍵時序參數

由于MIG無法使用當前JEDEC標準以外的參數創建接口邏輯,因此必須首先創建兼容JEDEC的DDR4控制器。

everspin 1Gb ST-DDR4 1333器件最類似于8Gb DDR4-2666 SDRAM器件,因此請使用8Gb DDR4 SDRAM 2666規格SDRAM DDR4-2666中的時序值,一旦創建了DDR4接口邏輯,就可以修改時序,上電,掉電和性能參數,以啟用ST-DDR4持久性存儲器。

強烈建議在創建MIG之后,在Vivado中創建一個示例測試臺,方法是右鍵單擊.xci文件并選擇名為“ Open IP Example Design ...”的菜單項。創建示例設計將創建一個新的Vivado項目。以及模擬新創建的MIG所需的所有測試文件。請參見Xilinx MIG創建教程,使用Vivado MIG為UltraScale設計存儲器接口和控制器,以及存儲器接口設計中心-UltraScale DDR4/DDR4存儲器。

本文關鍵詞:everspin STT-DDR4

相關文章:?everspin非易失性存儲器MR4A16B

深圳市英尚微電子有限公司是一家專業的靜態隨機記憶體產品及方案提供商,十年來專業致力代理分銷存儲芯片IC, SRAM、MRAM、pSRAM、 FLASH芯片、SDRAM(DDR1/DDR2/DDR3)等,為客人提供性價比更高的產品及方案。

英尚微電子中國區指定的授權代理:VTI、NETSOL、JSC濟州半導體(EMLSI)、Everspin 、IPSILOG、LYONTEK、ISSI、CYPRESS、ISOCOME、PARAGON、SINOCHIP、UNIIC; 著名半導體品牌的專業分銷商 如:RAMTROM、ETRON、FUJITSU、LYONTEK、WILLSEMI。

?更多資訊關注SRAMSUN. www.sjbg.net.cn 0755-66658299